Quantum error correction remains the central bottleneck separating present-day quantum hardware from fault-tolerant, large-scale quantum computation. While theoretical thresholds are well understood, their practical realization has proven costly, largely because conventional qubit-based codes demand substantial physical overhead to suppress errors to algorithmically useful levels. Over the past decade, this challenge has motivated renewed interest in bosonic quantum error-correcting codes, which encode logical information directly into high-dimensional harmonic oscillators rather than into arrays of two-level systems. By exploiting the structure of oscillator Hilbert spaces, bosonic encodings promise a fundamentally different route toward hardware efficiency. Among bosonic approaches, cat codes have emerged as particularly compelling. Their defining feature is a strong noise asymmetry: common physical error processes such as photon loss predominantly induce phase-flip errors, while bit-flip errors are exponentially suppressed as the separation between coherent states increases. This intrinsic noise bias opens the door to tailored error-correction strategies that exploit asymmetry rather than fighting it. In principle, if this bias can be preserved during gate operations, it enables surface-code-like architectures with dramatically reduced overhead. The difficulty, however, lies in turning this promise into a scalable architecture. Bias-preserving entangling gates between bosonic modes are experimentally demanding and often impose severe constraints on coherence, engineered dissipation, or Hamiltonian complexity. At the same time, purely bosonic processors struggle with fast, high-fidelity syndrome extraction and readout. As a result, previous demonstrations of cat-based error correction have largely remained limited to repetition-code-style protection against a single dominant error channel. To this end new research paper published in PRX Quantum and led by Professor Oskar Painter, and Fernando Brandão from the Division of Physics, Mathematics and Astronomy at California Institute of Technology, the researchers developed a scalable hybrid quantum error-correction architecture that combines dissipatively stabilized cat qubits with transmon ancillas. They introduced a practical cat-controlled entangling gate that enables correction of residual bit-flip errors while preserving exponential noise bias.

The research team develops and analyzes the hybrid cat–transmon architecture through detailed theoretical modeling and numerical simulation, with particular attention to gate-level noise processes and their impact on logical performance. Cat qubits are encoded in two-component superpositions of coherent states stabilized via engineered dissipation, ensuring confinement to the logical manifold and establishing a strong intrinsic noise bias. These storage modes are coupled dispersively to transmon qubits, whose excited-state structure is leveraged to mediate entangling operations and syndrome extraction.

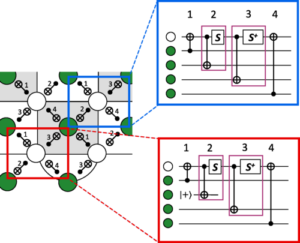

Two classes of cat–transmon gates form the operational backbone of the architecture. To address the dominant phase-flip errors on the cat qubits, the authors employ a transmon-controlled gate realized through free evolution under the dispersive interaction. This gate is simple, fast, and experimentally well aligned with existing superconducting circuit techniques. Although it does not preserve noise bias exponentially, careful use of higher transmon levels renders it sufficiently biased to avoid catastrophic error propagation. The more subtle challenge lies in correcting the exponentially suppressed but nonzero bit-flip errors of the cat qubits. To this end, the work introduces a cat-controlled transmon rotation implemented via a composite pulse sequence involving coherent displacements and number-selective transmon drives. Numerical simulations show that this gate achieves exponential suppression of cat bit-flip errors with increasing cat amplitude, even in the presence of realistic decoherence. Echo techniques and tailored pulse shaping are used to mitigate both dephasing-induced errors and coherent leakage arising from finite pulse durations. The authors quantified gate performance using master-equation simulations that incorporate photon loss, dephasing, transmon relaxation, and heating within a unified noise model. Across a broad parameter regime compatible with state-of-the-art devices, both classes of gates achieve infidelities below the 10⁻³ level while maintaining effective noise biases in the range of 10³–10⁴. Importantly, these values are obtained without requiring exceptionally strong engineered dissipation or exotic Hamiltonian engineering. Afterward, the authors simulate full surface-code cycles using circuit-level noise models. Rectangular surface codes are employed to exploit the asymmetric error structure, with shorter distances allocated to the already suppressed error channel. Logical memory simulations demonstrate exponential suppression of logical errors below a threshold compatible with near-term coherence parameters. In the deep subthreshold regime, the architecture achieves target logical error rates with qubit counts that are several times smaller than those required by unbiased-noise architectures operating at comparable physical error rates.

In conclusion, the new work of California Institute of Technology scientists allowed surface-code operation with dramatically reduced qubit overhead using experimentally realistic parameters. It redefined what hardware efficiency means for fault-tolerant quantum computing. Rather than pursuing maximal noise bias at all costs, the hybrid cat–transmon architecture shows that carefully balancing bias preservation with operational simplicity can yield comparable—or even superior—system-level performance. This insight is particularly important at a stage where experimental feasibility, integration complexity, and reliability matter as much as asymptotic thresholds. One immediate implication is that bosonic codes need not function in isolation to deliver their benefits. By embedding cat qubits within a mixed hardware ecosystem that includes transmons, the architecture leverages decades of progress in superconducting qubit control while retaining the exponential error suppression intrinsic to bosonic encodings. This division of labor reduces pressure on any single component to perform optimally across all tasks, a principle that mirrors successful strategies in classical fault-tolerant engineering. From a resource perspective, the demonstrated reduction in logical qubit overhead is striking. Achieving logical error rates relevant for algorithms with only a few hundred physical components places fault-tolerant quantum memory within a regime that is at least conceptually compatible with near-term multi-module devices. Importantly, the comparison drawn in the study shows that this performance would otherwise require physical error rates one to two orders of magnitude lower in unbiased architectures—levels that remain beyond current transmon technology.

The work also has broader methodological implications. By rigorously connecting gate-level noise bias to surface-code performance through detailed simulations, it provides a template for evaluating other hybrid or biased-noise platforms. The analysis highlights that thresholds alone are insufficient metrics; deep-subthreshold behavior and overhead scaling ultimately determine architectural viability. Looking forward, the hybrid approach suggests multiple avenues for refinement. Improvements in transmon coherence directly translate into higher effective bias ceilings, while advances in pulse optimization and dissipation engineering could further suppress residual errors. Moreover, the architecture is not tied to a specific surface code variant, leaving room for exploration of alternative biased-noise codes or decoder strategies. In sum, this study reframes the path toward fault-tolerant quantum hardware. It demonstrates that scalability need not rely on idealized components or extreme parameter regimes, but can emerge from architectures that intelligently combine complementary physical strengths. As such, it represents a substantive step toward making quantum error correction not just theoretically sound, but practically attainable.

Reference

Connor T. Hann, Kyungjoo Noh, Harald Putterman, Matthew H. Matheny, Joseph K. Iverson, Michael T. Fang, Christopher Chamber and Oskar Painter, and Fernando G.S.L. Brandão. Hybrid Cat-Transmon Architecture for Scalable, Hardware-Efficient Quantum Error Correction. PRX Quantum 6, 030305 – Published 11 July, 2025

Go to Journal of PRX Quantum.

Advances in Engineering Advances in Engineering features breaking research judged by Advances in Engineering advisory team to be of key importance in the Engineering field. Papers are selected from over 10,000 published each week from most peer reviewed journals.

Advances in Engineering Advances in Engineering features breaking research judged by Advances in Engineering advisory team to be of key importance in the Engineering field. Papers are selected from over 10,000 published each week from most peer reviewed journals.